Finite State Machine Serial Adder

Abstract— Logic design is in itself bifurcated to- Combinational and Sequential circuits. The later has memory and former doesn’t, so in an advent effort to incorporate memory into a combinational circuit brought in the concept of Finite state machine serial adder.

Keywords— D-latch, Finite state machine, Mealy Model, Multisim, Serial adder

I. INTRODUCTION TO FINITE STATE MACHINE

A finite state machine can be represented by a state transition table or a state diagram. There is often a fixedstart state which is the initial state of the Finite State Machine (before any input has been read). Thus a finite state machine (FSM) is a model describing the behavior of a finite number of states, the transitions between those states, and actions [1].

II. SERIAL ADDER

The serial binary adder or bit-serial adder is a digital circuit that performs binary addition bit by bit. The serial full

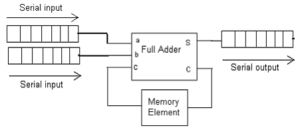

adder has three single-bit inputs, two for addition and one for carry in(C-in). There are two single-bit outputs for the sum and carry out(C-out). The C-in signal is the previously calculated C-out signal. Adding each bit, lowest to highest, one per clock cycle, performs the addition [2]. Fig 1 shows a basic structure of a FSM serial adder.

Fig 1: Block diagram of a serial adder[2]

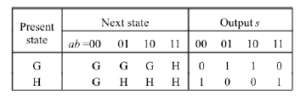

The design is based on Mealy model. Let us consider two states, G & H i.e. when carry is generated we take H state &

when carry is zero we take G state. A & B are taken as the inputs to the serial adder. Table 1 shows the state table of the serial adder [2].

Table 1: STATE TABLE of SERIAL ADDER[2]

Based on the state table we can construct the state diagram. The state diagram is as shown in Fig 2. As observed in the state figure as long as the there is no carry generated, it stays in state G. but if there is a carry generated, it immediately moves to state H. In this state carry is added to the sum. When sum of A & B does not create a carry it moves back to state G.